著者・講師:圓山 宗智/Munetomo Maruyama

企画編集・主催:ZEP エンジニアリング株式会社

CoreStaffONLINEで取扱いのある米国のFPGAメーカーのエフィニックス(Efinix)について FPGAスタータキット“Xyloni”の入門[導入編]として、Efinix社のコンパクトなTrion FPGAを搭載した超小型ボードXyloniを使って、開発環境のインストールから、簡単な論理回路の設計とFPGAへの実装までを具体的に解説いたします。

前半ではFPGAメーカーのEfinix社のご紹介から超小型開発ボード“Xyloni”について解説していきます。

〈コアスタッフ〉

目次

1 新たなる FPGAメーカ Efinix 社の登場

高性能で多機能なシステムを開発する場合、汎用マイコンを使って最近の高度化したAI処理などを実現するには性能が不足し、カスタマイズしたくなることがあります。

そのようなケースで、CPUを含むさまざまな論理回路を実現するために新規に SoC(System On a Chip)を開発しようとすると、膨大な開発費と工数がかかります。

また、さまざまなシステム開発の初期段階において実機による原理試作をしたい場合も、SoCを試作するにはやはり費用と工数が壁になります。

こうしたケースにおいては、FPGA(Field Programmable Gate Array)ほど手軽で柔軟なデバイスは他にありません。

FPGAの中では自分が設計した論理回路がそのまま動作しますので、自由気ままなハードウェア作りを楽しめます。

凝りに凝ったオリジナルRISC-V CPUコアを造る、超高速並列演算回路を組む、エッジAI処理を高速化する回路を組む、液晶ディスプレイを接続してグラフィック制御装置を造る、既存の汎用マイコンと組み合わせて機能拡張する、などなど無限の可能性が広がります。趣味で論理回路を自作して楽しむ場合も、FPGAはとても便利に使えます。

これまでのFPGAは、米Intel社(旧・米Altera 社) と米AMD社(旧・英 Xilinx社)の大手2社が有名でした。

大規模 FPGAから低コストFPGAまでの幅広い製品を展開しています。

こうした中、2012年に新たなFPGAメーカが誕生しました。

それが米Efinix社(図1)です。

Efinix社の汎用FPGA 製品は、現在2シリーズ展開されており、モバイルやIoT向けの小~中規模なTrion FPGAシリーズと、機械学習を含む高度なコンピューティング向けの中規模~大規模なTitanium FPGAシリーズがあります。

いずれも独自のQuantumファブリック技術により、従来のFPGA製品よりも、電力・性能・面積で大幅な改善を図っているようです。

さらに Efinix社は、最近幅広く使われるようになったオープンソース命令セットのRISC-Vを開発プラットフォームとして精力的に整備しており、無償でカスタマイズ可能なマイコンやプロセサをFPGA上で容易に実現できます。

Efinix社はこうしたアクティビティも楽しみなFPGAメーカだといえるでしょう。

Efinix社は、自社のFPGAブロックを、IPコア(Intellectual Property Core:回路部品) としてSoCベンダに供給するビジネスも展開しています。

SoCに、ハードで固定化した機能だけでなく、FPGAによるフレキシビリティも搭載することができ、応用の幅を従来以上に拡大できることになります。

ここで特徴的なのが、Efinix社は、他社とは異なり、製造するファウンドリのプロセスをカスタマイズすることなく標準 CMOSプロセスを使っている点です。

FPGAブロックが他のファウンドリのプロセスへの移植が容易と考えられるので、SoC設計者にとってファウンドリが固定されない点もメリットになっていくでしょう。

また、Efinix社にとっても、コストメリットがある生産工場に移りゆくことができると思われます。

ちなみに、半導体不足だった折、Efinix社の製品は、ファウンドリのカスタム工程を使わずに済んだので、生産が滞ることがなかったそうです。

そのFPGAで最も重要な要素が開発環境です。

Efinix社はFPGAの論理設計用の統合化開発環境Efinity IDEを無償で提供しています。

またFPGAにRISC-Vコアを搭載した場合のソフトウェア統合開発環境 Efinity RISC-V Embedded Software IDEも無償提供しています。

本稿では、Efinix社のコンパクトなTrion FPGAを搭載した超小型ボード Xyloniを使って、開発環境のインストールから、簡単な論理回路の設計とFPGAへの実装までを具体的に解説します。※1

※1 本記事に記載されている社名および製品名は、一般に開発メーカーの登録商標または商標である。 本文中では TM、Âő、Âľ の各表示を明記していない。

2 Efinix社のFPGA技術と製品

2.1 ゲートと配線のバランスを最適化する基本技術「Quantum ファブリック」

Efinix社のFPGA製品のロジック・セルの基本構造は、独自技術Quantumファブリックをベースにしています。

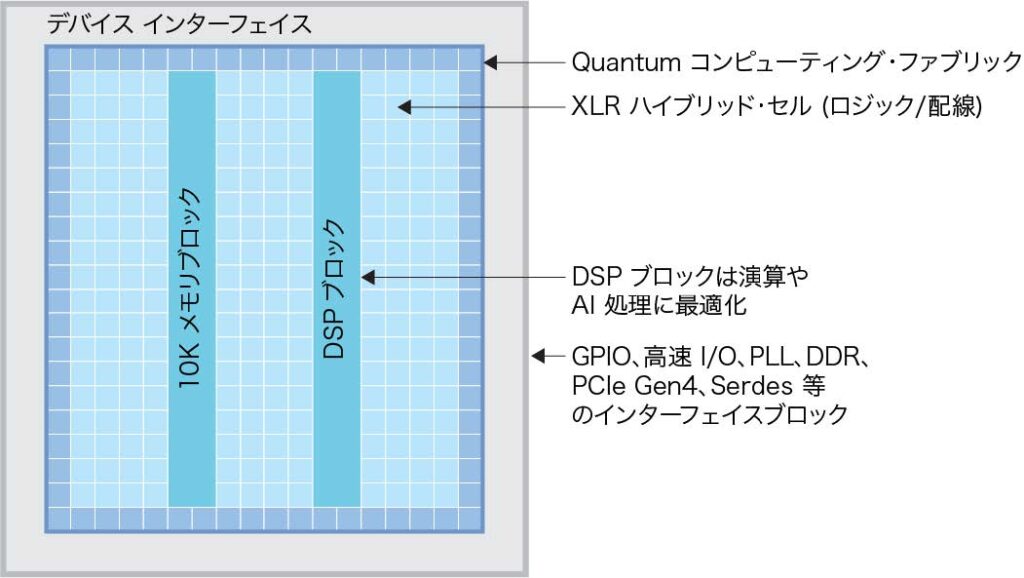

Quantumファブリックの基本的な構成要素は、図2に示すようなXLR(eXchangeable Logic and Routing)セルです。

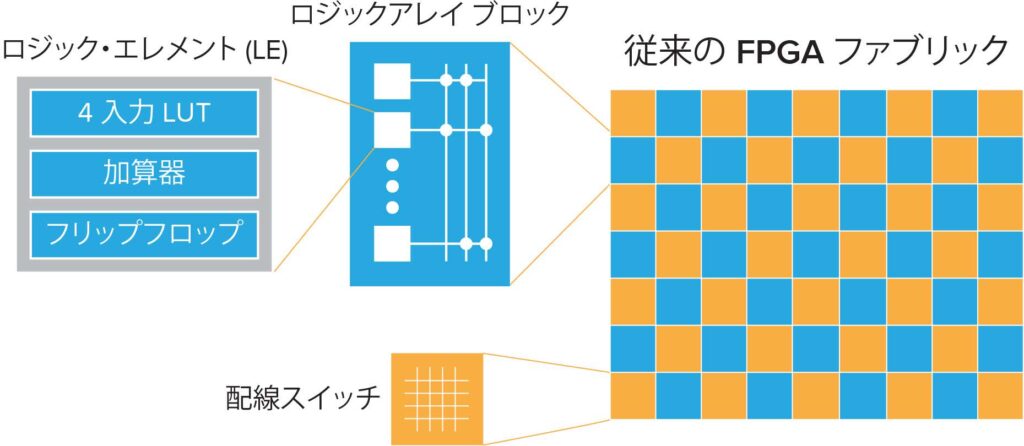

従来のFPGAの回路構造を図3に示します。

従来は、ロジック・セルとインターコネクト(配線スイッチ)が独立していました。

このため、ゲート量と配線量のバランスによってFPGA全体のリソース利用効率が悪くなるケースがありました。

特に論理規模が大きくなるほど、配線の割合が増えてしまい、ロジック・セルが余っているにもかかわらず、配線が混雑して配置配線が閉じなくなることがあり、FPGA活用時の悩みの種でした。

Efinix社のXLRセルは、LUT(LookUp Table)ベースのロジックセルおよび配線スイッチのいずれとしても機能します。

この構造により、ゲート過多の設計に対しても、配線過多の設計に対しても、ロジックと配線を柔軟に再構成し、インターコネクトの接続性を高めることができます。

また、XLRセルのロジック・セルは、複数の機能に変化(FPGA 製品シリーズに依存するが、例えば、単一のLUTを複数のLUT に分割したり、加算器にしたり、シフト・レジスタに設定するなど)できるので、より効率的に論理回路構造を構築することができます。

結果として、Quantumファブリックは、(1) 面積を1/2~1/4に削減可能、(2) 消費電力を1/2以下に削減可能、(3) 100万LE(Logic Element)以上まで拡張可能、(4) 幅広なデータバスを構成可能、(5) データのパイプライン化が容易、(6) 全てCMOSパス・ゲートで実現しており、シリコン・プロセスに依存しない、といったメリットがあります。

※1 Efinix 社ホームページから引用。

2.2 小~中規模なTrion FPGA製品シリーズ

Trion製品シリーズは、モバイルや IoT 向けの小~中規模なFPGAで 40nmプロセスで製造されています。

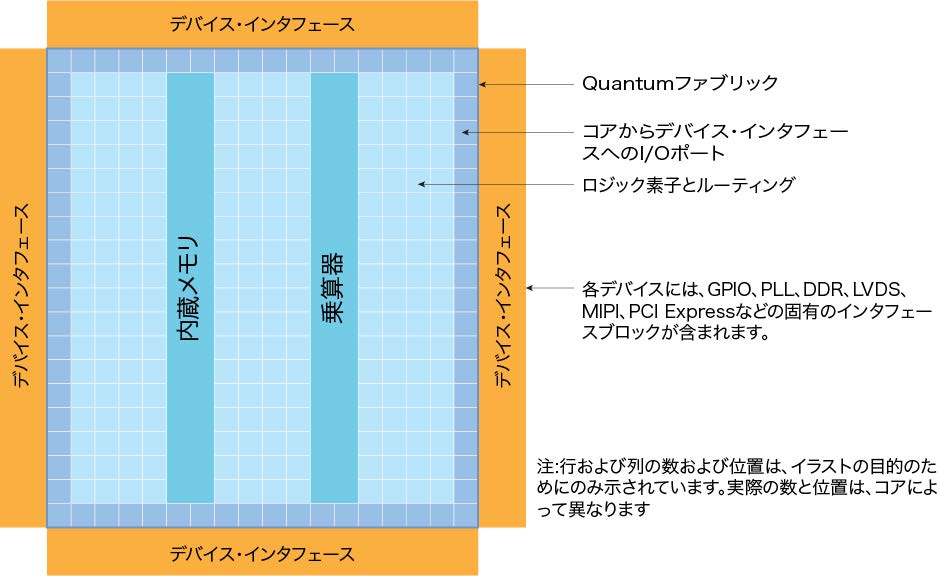

Trion FPGA の内部構造を図4に示します。

プログラマブル・ロジックとルーティング配線はQuantumテクノロジをベースにファブリックとして構成され、内部に内蔵メモリや乗算ブロックを含み、その回りにI/Oインターフェースが配置されています。

機能 |

T4 |

T8 |

T13 |

T20 |

T35 |

T55 |

T85 |

T120 |

|---|---|---|---|---|---|---|---|---|

ロジック・エレメント (LE) |

3,888 |

7,384 |

12,828 |

19,728 |

31,680 |

54,195 |

84,096 |

112,128 |

マスク・プログラマブル |

✓ |

✓ |

✓ |

✓ |

― |

― |

― |

― |

内蔵メモリ・ビット (kb) |

77 |

123 |

727 |

1,044 |

1,475 |

2,765 |

4,055 |

5,407 |

18×18 乗算器 |

4 |

8 |

24 |

36 |

120 |

150 |

240 |

320 |

PLL |

1 |

5 |

5 |

7 |

7 |

8 |

8 |

8 |

最大 GPIO 本数2 |

55 |

97 |

195 |

222 |

222 |

278 |

278 |

278 |

LVDS (TX, RX) |

― |

6, 6 |

13, 13 |

20, 26 |

20, 26 |

52, 52 |

52, 52 |

52, 52 |

DDR3, LPDDR3, LPDDR2 |

― |

― |

― |

x16 |

x16 |

x32 |

x32 |

x32 |

MIPI DPHY (4 レーン) |

― |

― |

2 RX |

2 RX |

2 RX |

3 RX |

3 RX |

3 RX |

Trion 製品シリーズのラインアップを表1に示します。ロジック・エレメントの規模は、3,888個から112,128個まで用意されています。

I/Oインターフェースは一般的なLVTTLインターフェースに加え、以下のインターフェースをサポートしています。

- MIPI: MIPI D-PHY(4 レーン) およびCSI-2 コントローラをハードIPとして実装。PHY当たり最大6Gbps。

- LVDS: 最大 800Mbps をサポート。

- DDR: DDR3、LPDDR3、およびLPDDR2をサポート。最大1,066MbpsのDDR 信号レート、最大51.2Gbpsの帯域幅で使用可能。DDR専用PHYおよびコントローラはハードIPとして実装。

Trionシリーズのうち小規模側の製品では、MPM(Mask Program Memory)をサポートしています。

FPGAのコンフィグレーション・データは通常、外部のシリアル・フラッシュ・メモリに記憶されますが、MPMではFPGA内部のオンチップ・マスクROMに記憶します。

FPGAのコストが低減し、かつ部品点数を削減できるので、低コスト化が要求される大量生産用途に活用できます。

TrionシリーズのパッケージはFBGAとLQFPで供給されています。

FBGAは、49ボールの 3mm □ (0.4mmピッチ) から 576 ボールの 16mm □ (0.65mm ピッチ) まで製品規模ごとに多くの種類がサポートされています。

LQFPは、144ピンの 20mm □ (0.5mm ピッチ) がT8とT20に用意されています。

※1 Efinix社ホームページから引用。

※2 MIPIおよびDDRインターフェースは専用のI/Oを使用するので、最大GPIO本数は、それらのインターフェースのI/O数を含まない。

2.3 中規模~大規模なTitanium FPGA製品

Titanium製品シリーズは、機械学習を含む高度なコンピューティング応用や高性能産業機器・通信機器向けの中規模~大規模なFPGAで16nmプロセスで製造されています。

Titanium FPGAの内部構造を図5に示します。

Titanium FPGAも、プログラマブル・ロジックとルーティング配線はQuantumテクノロジをベースにしています。

最大100万規模のLEと、大容量メモリ、およびAI 処理に最適化したDSPブロックを内蔵した高性能ファブリックを搭載し、その周囲にI/Oインターフェースが配置されています。さらにハード化されたRISC-Vコアを4個内蔵した製品も展開しています。

機能 |

Ti35 |

Ti60 |

Ti90 |

Ti120 |

Ti180 |

Ti240 |

Ti375 |

Ti550 |

Ti750 |

Ti1000 |

|---|---|---|---|---|---|---|---|---|---|---|

ロジック・ |

36,176 |

62,016 |

92,534 |

123,379 |

176,256 |

236,888 |

370,137 |

533,174 |

727,056 |

969,408 |

10K |

1.53 |

2.62 |

6.88 |

9.18 |

13.11 |

19.37 |

27.53 |

39.65 |

54.07 |

72.09 |

DSP |

93 |

160 |

336 |

448 |

640 |

946 |

1,344 |

1,936 |

2,640 |

3,520 |

PLL |

4 |

4 |

10 |

10 |

10 |

10 |

10 |

10 |

10 |

10 |

GPIO |

34 |

34 |

80 |

80 |

80 |

80 |

80 |

80 |

80 |

80 |

高速 |

146 |

146 |

232 |

232 |

232 |

172 |

172 |

268 |

268 |

268 |

DDR4, |

― |

― |

x32 |

x32 |

x32 |

x72 |

x72 |

2 x72 |

2 x72 |

2 x72 |

MIPI |

― |

― |

4 RX |

4 RX |

4 RX |

3 RX |

3 RX |

3 RX |

3 RX |

3 RX |

16Gbps |

― |

― |

x8 |

x8 |

x8 |

x12 |

x12 |

x16 |

x16 |

x16 |

25.8 |

― |

― |

― |

― |

― |

― |

― |

x8 |

x8 |

x8 |

内蔵 |

― |

― |

― |

― |

Quad |

Quad |

Quad |

Quad |

Quad |

Quad |

PCI |

― |

― |

1×4 |

1×4 |

1×4 |

2×4 |

2×4 |

2×8 |

2×8 |

2×8 |

Titanium 製品シリーズのラインアップを表2に示します。

ロジック・エレメントの規模は、36、176 個から 969,408個という大規模な数まで用意されています。

I/Oインターフェースは Trion シリーズに対し大幅に強化されており、DDR4/LPDDR4、高速SerDes、PCI Expressなどもサポートしています。 Ti180以上の製品にはハード化されたQuadコアのRISC-Vも内蔵しています。

Titanium シリーズのパッケージは、FBGA と WLCSP で供給されています。

FBGA は、100 ボールの 5.5mm□ (0.5mm ピッチ) から 1,156 ボールの 35mm □ (1.0mm ピッチ) まで製品規模ごとに多くの種類がサポートされています。

小型の WLCSP は、64ボールの 3.5mmx3。4mm(0.4mm ピッチ) がTi60に用意されています。

※1 Efinix社ホームページから引用。

3 Efinix 社のFPGA開発環境

FPGAで自分の論理回路を設計するとき、最も重要なのが開発環境です。

その使い勝手がそのままFPGAの良し悪しを決めると言っていいでしょう。

FPGAの論理設計向けとして、論理合成、配置配線、タイミング解析、コンフィグレーションまでのフローを一貫して開発できる統合化開発環境 Efinity IDE が無償て提供されています。

またFPGAにRISC-Vコアを搭載した場合のソフトウェア統合開発環境 Efinity RISC-V Embedded Software IDEも無償提供されています。

本稿では、これらの開発ツールのインストール方法から使い方まで詳細に説明します。

3.1 FPGA統合化開発環境 Efinity IDE

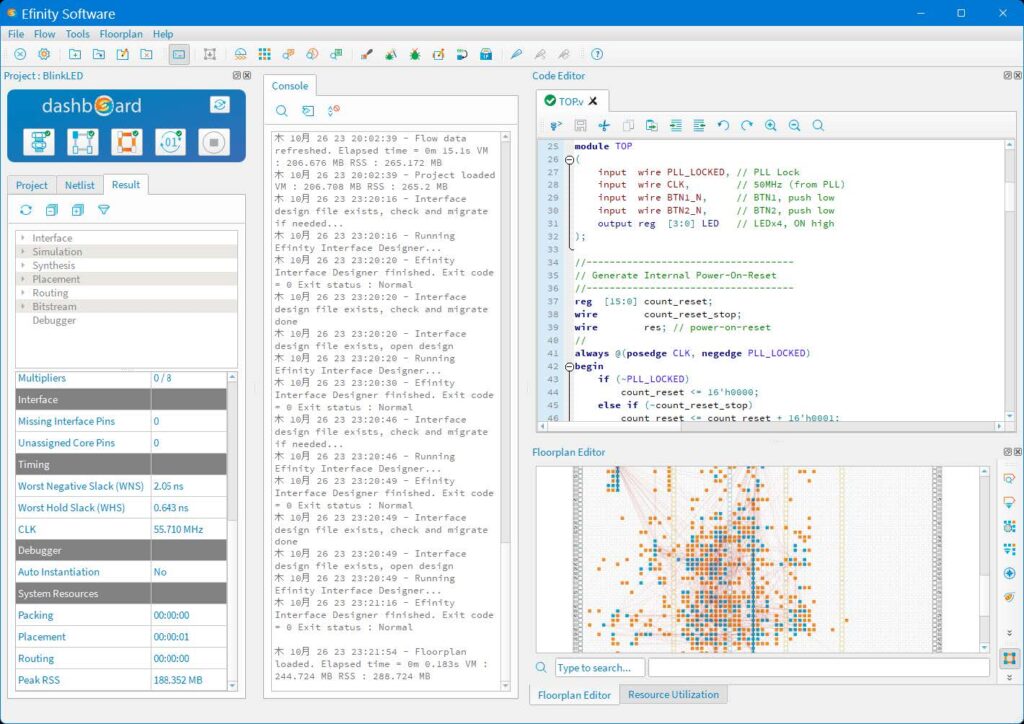

Efinix 社のFPGAでシステム開発する際に最も重要かつ基本となるツールが統合化開発環境Efinity IDEです。

無償で提供されており、論理シミュレーション、論理合成、配置配線、タイミング解析、コンフィグレーションまでのフローを一貫して実行します。

論理シミュレーションは、外部ツールを使います。デフォルトで無償のVerilog シミュレータIcarus Verilogをサポートします。

これ以外に、独Siemens社のModelSimや米Cadence社のNCSimもサポートしています。

Efinity IDEの画面の例を図6に示します。

Efinix 社は、そのFPGAの中に組み込んで使える多くのIPコアも提供しています。

演算コア、内部バス、内部メモリ、外部メモリ・インターフェース、通信インターフェースなどがあります。

RISC-V SoCも提供されており、オリジナルのカスタム・マイコンとして仕立てることも容易になっています。

Efiniy IDEには多くの機能が搭載されています。その一部を以下に示します。

- プロジェクト管理

- Verilog HDL、SystemVerilog、および VHDL 言語をサポート

- 無償の Icarus Verilog、または ModelSim や NCSim による論理シミュレーションをサポート

- FPGA の外部とのインターフェース部(I/O 端子や PLL など)を定義するインターフェイス・デザイナ

- 各設計フローの実行制御(論理合成、配置、配線、ビットストリーム生成)

- デザイン階層、レポートファイル等のグラフィカル表示

- フロアプラン・エディタ

- タイミング解析ツール

- デバッグのためのロジック・アナライザ機能

- FPGA コンフィグレーション用のプログラマ機能

Efinix 社のFPGAを設計する際の考え方については少し注意が必要です。

従来のFPGAでは、最上位階層のRTL記述にFPGAの外部端子を含めて全て記述していました。

そのRTL記述にはI/Oバッファを想起させる記述を書き、その詳細属性(端子位置、ドライブ強度、プルアップ抵抗の有無など)は制約として個別に設定していました。

また内蔵PLLはIPブロックとして個別に定義して RTL記述内にインスタンス化していました。

一方、Efinity IDEの思想は従来とは異なり、外界とインターフェースするデバイス・インターフェースと内部ファブリック論理の部分を明確に分けて設計します。

デバイス・インターフェースには、入出力端子、PLL、ユーザ向けJTAGインターフェース(例えばRISC-Vのデバッガ・インターフェースになるもの)などが含まれます。

これらは、Efinity IDEのインターフェース・デザイナで定義し、デバイス・インターフェースと内部ファブリックの間に行き交う信号を定義します。

そしてユーザが設計する最上位階層のRTL記述の入出力信号としては、そのデバイス・インターフェースと内部ファブリックの間の信号を記述します。

すなわち、ユーザが記述する最上位階層のRTL記述よりもさらに上位階層にインターフェース・デザイナで定義した回路が存在することになります。

例えば、双方向の外部端子においては、ユーザが記述する最上位階層のRTL記述には、I/Oバッファからの入力信号、I/Oバッファへの出力信号、I/Oバッファの出力ドライブ制御信号(アウトプット・イネーブル)の3つの信号を記述する必要があります。

よって、論理シミュレーションの段階では、そのテストベンチ記述の中で、ユーザが書いた最上位階層のRTL記述をインスタンス化しますが、同時にそのテストベンチ内にはインターフェース・デザイナで定義した機能も盛り込む必要があります。

例えば、双方向の外部端子についてはその信号をテストベンチ内に定義し、出力ドライブ制御信号(アウトプット・イネーブル)によりドライブするかHi-Zにするかをテストベンチ内で制御させて検証する必要があります。

PLL が作るクロックのテスト・ベンチ内にモデルとして記述して論理シミュレーションを実行することになります。

この考え方には好き嫌いが出る面があるかもしれません。

しかし、FPGAの外界とのインターフェース部分を整理しながらまとめて一箇所で設計できるので、従来のFPGAのようにツールのあちこちで制約指定する必要がなく、見通しがよくなり間違いが起きにくい方法だといえるでしょう。

これらの設計方法の詳細は、本稿の設計事例の項で説明します。

3.2 RISC-V 統合化開発環境 Efinity RISC-V Embedded Software IDE

RISC-Vは命令セットがオープン化されたCPU アーキテクチャであり、誰もが自由に設計できます。

そのため、従来のARMのように1社にCPUが独占されることがなくなり、現在では多くの実装がカスタマイズ含め存在し、加速度的に普及が拡大しています。

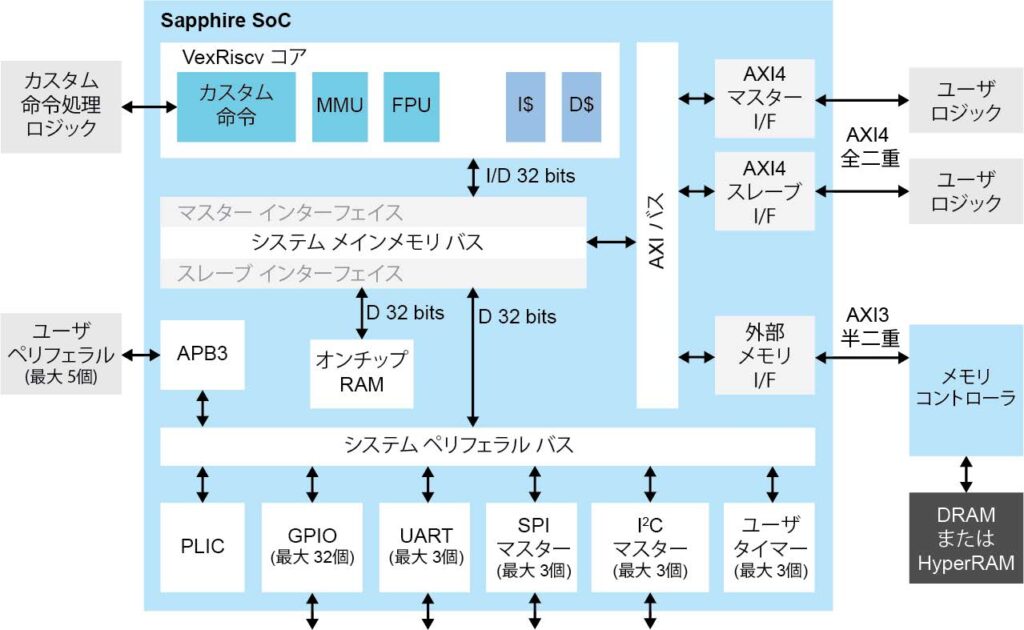

Efinix 社も、CPUコアと周辺機能を含む IP としてSapphire RISC-V SoCを提供しています。

ブロック図を図7に示します。さまざまなカスタマイズをサポートするツールも用意されています。

このIPをFPGAに組み込むことで、好きな仕様のマイコンやシステム LSIを実現することができます。

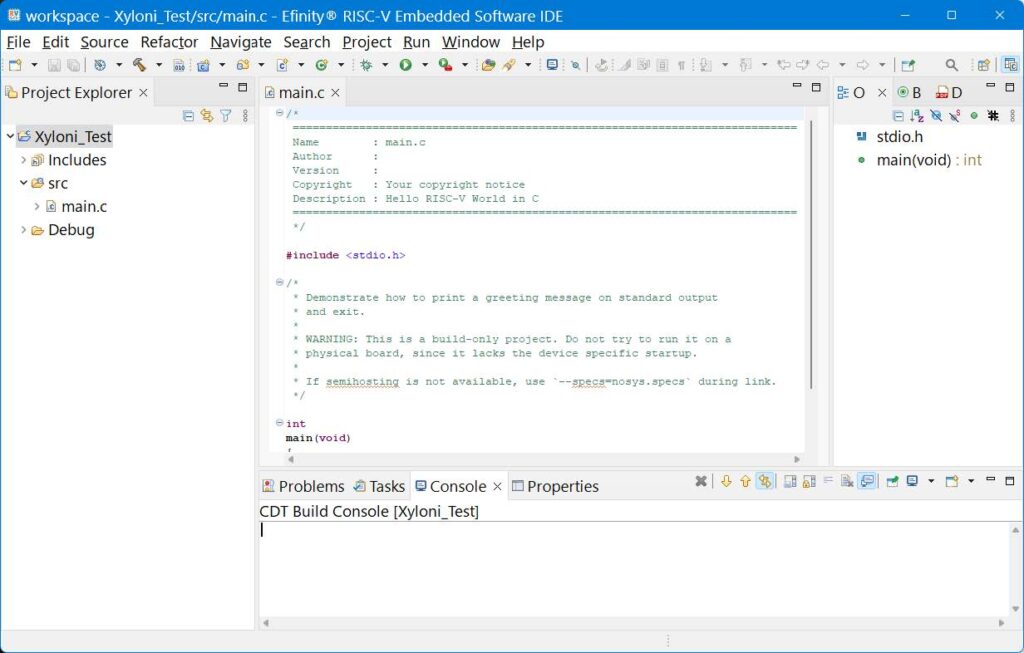

このRISC-Vのソフトウェアを開発しデバッグするための統合化開発環境がEfinity RISC-V Embedded Software IDEで、これも無償提供されています。

画面の例を図8に示します。

C/C++言語のソース・コード編集から、プログラムのビルド、エミュレータによるシミュレーション、実機へのダウンロードとデバッグを行なえます。

内容としてはオープンなEclipseベースの統合開発環境に、GNUツール・チェーンと OpenOCDを統合したものであり、RISC-V向けとしてはとても標準的で実績があるものです。

※1 Efinix社ホームページから引用。

4 超小型開発ボード Xyloni

FPGAを手軽に使いたいときは、既成の評価用ボードを活用するのが便利です。

Efinix社もTrion FPGAとTitanium FPGAそれぞれが搭載された評価用ボードやI/O拡張ボードなどを多く準備しています。

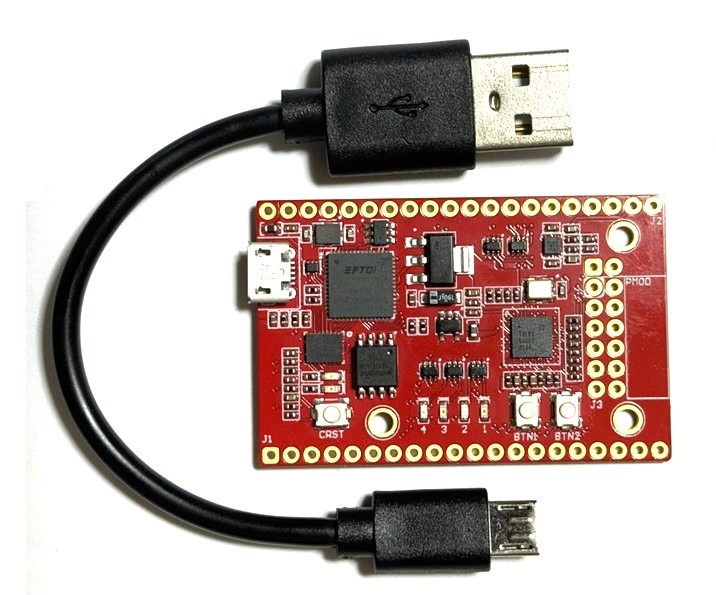

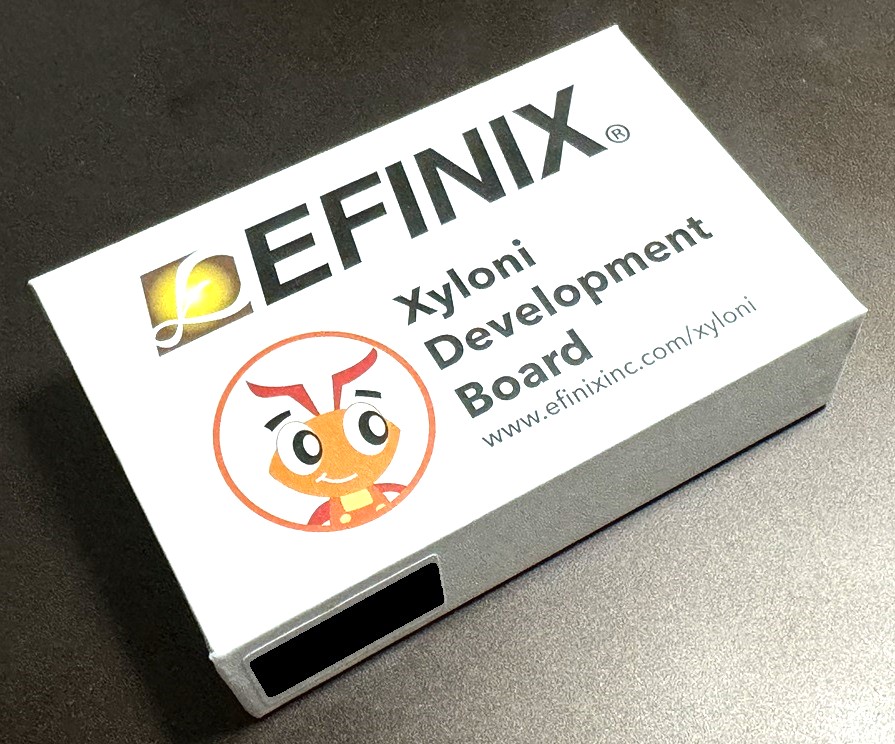

その中で異彩を放つのがマッチ箱サイズのXyloniです。

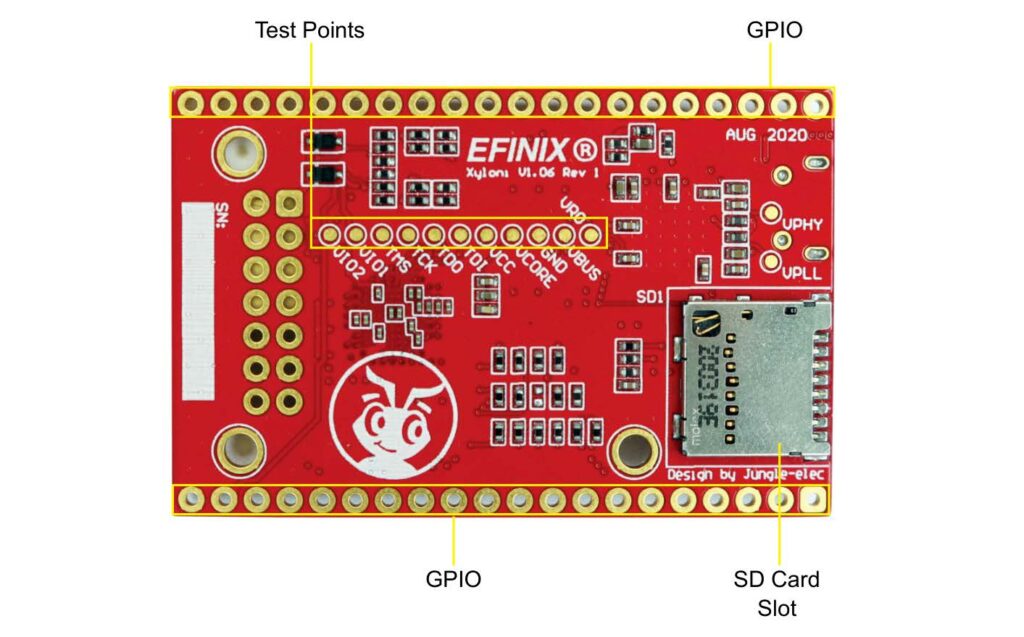

ボード本体とその外箱をそれぞれ図9と図10に示します。

ボード・サイズはわずか50mm×33mmと小さく、趣味や簡単な実験など手軽に扱うことができます。

本稿では、Xyloniを使った設計事例を紹介します。

Xyloniの箱と基板(裏面)には、赤いアリさんのキャラクタが描かれていますが、調べてみると学名がSolenopsis xyloniというアリの仲間のようです。

基板の色と大きさになぞらえているのかもしれません。

4.1 Xyloni ボードの仕様概要

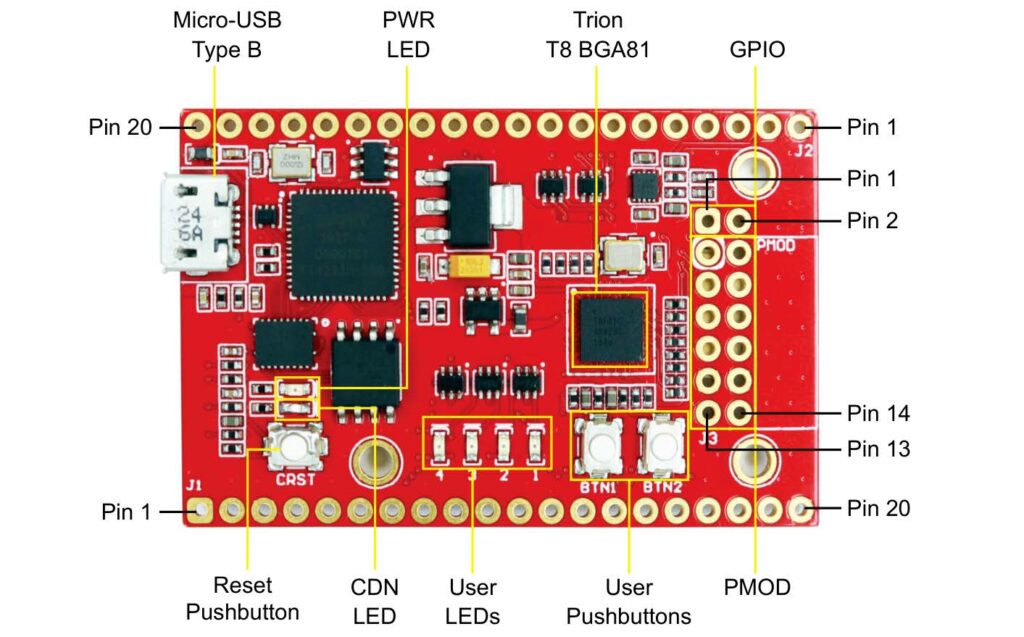

Xyloniボードは、Trion FPGAのT8を搭載しています。

パッケージは5mm □のFBGAで81ボール(0.5mmピッチ)あります。

ロジック・エレメントは 7,384個あり、77kbのメモリ、8個の乗算器 (18×18)、5個のPLLを内蔵しています。

趣味の電子工作や簡単な実験には十分な構成であり、またRISC-V SoCも搭載できるので、応用の幅はとても広いといえるでしょう。

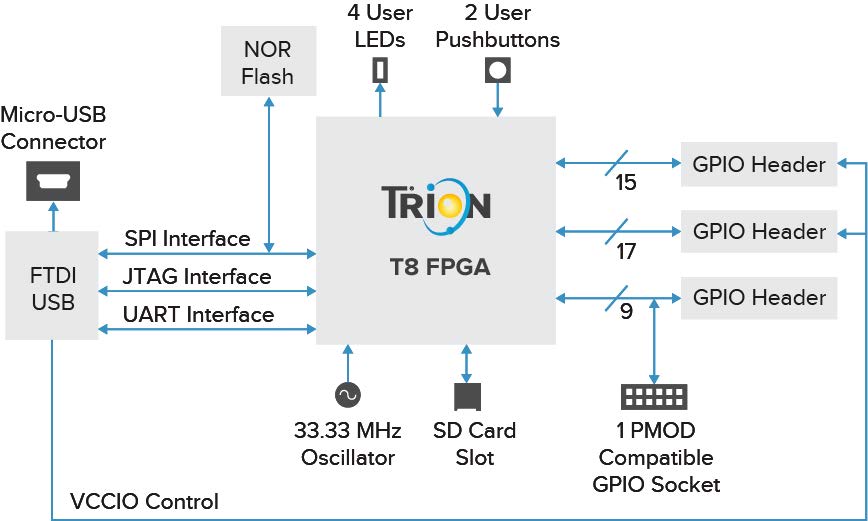

図11にXyloniボードのブロック図を示します。

Xyloniボードの仕様概要は以下のとおりです。

- Efinix Trion FPGA T8F81C2(81ボールFBGAパッケージ)

- 128Mbit SPI NOR FLASH メモリ(FPGAのコンフィグレーション用)

- USB コネクタ (mirco USB Type B) から、FPGAのコンフィグレーションやUART通信が可能

- GPIO ヘダー 40ピン

- PMOD 規格ヘダー 12 ピン(PMOD:米 Digilent 社が規定した低周波・少I/O本数のインターフェース)

- マイクロ SD カード・スロット

- ユーザ用 LED × 4個、ユーザ用プッシュ・スイッチ× 2個

- 33.33MHz 発振器

- I/O 電源電圧を USB 通信で設定可能(デフォルト 3.3V、他に2.5Vと1.8Vから選択可能)

4.2 Xyloni ボードのリソース

Xyloni ボードの部品配置について、表面を図12に、裏面を図13に示します。

ユーザ・インターフェースとして、表面にUSB コネクタ、コンフィグレーション用プッシュ・ボタン、ユーザ用プッシュ・ボタン(2個)、ユーザ用 LED(黄色× 4個)、裏面にSDカード・スロットが実装されています。

※1 Xyloni Development Kit User Guide から引用。

4.3 USBインターフェース

USBコネクタには、英 FTDI社のFT4232H-56Q(Hi-Speed Quad USB UART IC)が接続されており、下記4つのインターフェースを構成しています。

- FTDI interface 0 = SPI

- FTDI interface 1 = JTAG

- FTDI interface 2 = UART

- FTDI interface 3 = VCCIO 設定

FTDIの4つのUSBインターフェースそれぞれに対してPC上のUSBドライバが必要ですが、専用のlibusb-win32をインストールするのはInterface 0、1、3 のみです。

Interface 2はWindowsの標準ドライバを使います。

この件は、後述のツールのインストールの項で改めて説明します。

4.4 FPGA のコンフィグレーション

Xyloniボードの上でTrion T8 FPGAをコンフィグレーションする方法はいくつかありますが、Xyloniボードのデフォルトでは次の方法が取られます。

まず、PCからUSBを介してビット・ストリーム・データを送り、Xyloniボード上のSPI NOR FLASHメモリに書き込みます。

Trion T8 FPGAは、アクティブ・コンフィグレーション・モードに設定され、その起動時にNOR FLASHメモリを読み出して自分自身をコンフィグレーションします。

この他のコンフィグレーション方法としては、外部のマイコンなどからSPI 通信でコンフィグレーション・データを送信してもらうパッシブ・コンフィグレーション・モードと、JTAG端子からFPGAを直接コンフィグレーションするモードがあります。

Trion T8 FPGAのコンフィグレーションはCRESET信号をLowレベルからHighレベルに立ち上げると開始します。

Xyloniボード上ではCRESET信号はプルアップ抵抗とコンデンサによる簡単なパワーオン・リセット回路から生成されているので、SPI NOR FLASHメモリにコンフィグレーション・データが書かれた状態でXyloniボードのUSBケーブルから電源を印加すると、自動的にコンフィグレーションが始まります。

あるいは、ボード上のコンフィグレーション用プッシュ・ボタン CRSTを押すとCRESET信号がLowレベルになるので、Trion T8 FPGAをコンフィグレーション含めてリセットしたいときは CRSTボタンを押します。

SPI NOR FLASHメモリ内には複数のコンフィグレーション・データを格納でき、Trion T8 FPGAのCBSEL0端子とCBSEL1端子によって選択可能です。

詳細はXyloni Development Kit User Guide[20]を参照してください。

Xyloniボードのデフォルトでは、1種類のコンフィグレーション・データだけを選択する回路になっていますが、実験用としては問題にならないでしょう。

コンフィグレーションが完了するとCDONE端子(プルアップされたオープン・ドレイン端子)がHighレベルになり、ボード上のLED CDN(緑色)が点灯して、FPGA 内部のユーザ回路が動作開始します。

ただし、CDONEがHighレベルになってから実際のユーザ回路が動作可能になるまではtU SER(15us+CDONE端子のLowレベルからHighレベルまでの立上り時間) 以上待つ必要があります。

すなわち、この期間はユーザ回路をリセット状態にしておかなくてはなりません。

外部からリセット信号を入力する場合はCDONE信号がHighになった後もtU SERの期間はリセットをアサートし続けるようにしてください。

内部でリセット信号を生成する場合は、PLLのロック信号を使えますが、PLLがロックしてからtU SERの間は内部リセット信号をアサートし続ける回路が必要です。

この具体的な方法は後述する設計事例のところで説明します。

4.5 I/O 電源電圧の設定

Trion T8 FPGA(FBGA81ピン)のユーザ用I/O端子は、BANK1A、BANK1B、BANK2A、BANK2B の 4系統に分かれています。

このうちBANK1A、BANK1B の電源電圧は 3.3V 固定ですが、BANK2A、BANK2B の電源電圧は 3.3V、2.5V、1.8V のいずれかに設定できます。

デフォルトは 3.3V です。なお、BANK1Cもありますが、PLL 電源 (1.2V)用の1端子だけでユーザは使えません。

BANK2A、BANK2Bの電源電圧を変更するときは、PC上の Pythonスクリプトを起動してFTDI interface 3を介して設定できます。

詳細は、Xyloni Development Kit User Guide[20]を参照してください。

本稿ではデフォルトの 3.3Vのままで使います。

4.6 クロック発振器

Xyloniボード上には 33.33MHz のクロック発振器が搭載されています。

そのクロックはTrion T8 FPGAのPLLIN 端子(GPIOL_20)に接続されているので、内蔵PLLを使って好きな周波数のクロックを生成してFPGA内部で使うことができます。

4.7 I/O 信号のボード内結線

FPGAの各端子は、ボード上の各種リソースに接続されています。

クロック、LED、スイッチ関係の信号結線を表3に、基板両サイドのピンヘッダとの信号結線を表4と表5に、PMODピンヘッダとの信号結線を表6に、SDカード・スロットとの信号結線を表7にそれぞれ示します。

FPGA端子名には長い名前のものがありますが、ユーザ用の一般信号として扱う分には、最初のGPIOx_nnまでを見てFPGA開発環境の上で機能アサインすれば OKです。具体的なアサイン方法は設計事例の項で説明します。

端子の後半の名称はコンフィグレーション時に有効になる機能などです。

表3の中の LED3、LED4、BTN2 はピンヘッダ J2にも接続されていますので注意してください。

この3つとも、基板上でプルアップされており、起動時にすべてHighレベルにしておくことで、FPGAがアクティブ・コンフィグレーション・モードに設定されます。

表6に示すようにPMODのピンヘッダは14ピンありますが、市販のPMOD基板モジュールは12ピンです。

PMOS基板モジュールを差し込む時は、ピンヘッダJ3のうちPin1とPin2は空けて差し込むようにしてください。

〈圓山 宗智〉

種類 |

ボード上の |

FPGA端子名 |

I/Oバンク |

端子位置 |

備考 |

|---|---|---|---|---|---|

クロック |

クロック発振器 |

GPIOL_20_PLLIN |

BANK1B |

C3 |

33.33MHz |

ユーザ用 LED |

LED1 |

GPIOL_21_NSTATUS |

BANK1B |

B3 |

High で点灯 |

LED2 |

GPIOR_37_TEST_N |

BANK2B |

J6 |

High で点灯 |

|

LED3 |

GPIOR_16_CTRL7_CBUS1 |

BANK2A |

D7 |

High で点灯 |

|

LED4 |

GPIOR_17_CTRL6_CBUS2 |

BANK2A |

D8 |

High で点灯 |

|

ユーザ用プッシュ・ |

BTN1 |

GPIOR_02_RESERVED_OUT |

BANK2A |

C5 |

押すと Low |

BTN2 |

GPIOR_15_CBUS0 |

BANK2A |

C9 |

押すと Low |

種類 |

ボード上の |

FPGA端子名 |

I/Oバンク |

端子位置 |

備考 |

|---|---|---|---|---|---|

ピン・ヘッダ J1 |

Pin 1 |

VBUS |

|

|

5V |

Pin 2 |

VCC |

|

|

3.3V |

|

Pin 3 |

GND |

|

|

GND |

|

Pin 4 |

GPIOR_20_CLK5 |

BANK2B |

F8 |

|

|

Pin 5 |

GPIOR_21_CLK4_CBSEL1 |

BANK2B |

E7 |

|

|

Pin 6 |

GPIOR_22_CTRL5 |

BANK2B |

F7 |

|

|

Pin 7 |

GPIOR_23_CTRL4 |

BANK2B |

E6 |

|

|

Pin 8 |

GPIOR_24 |

BANK2B |

F6 |

|

|

Pin 9 |

GPIOR_25 |

BANK2B |

F5 |

|

|

Pin 10 |

GPIOR_26_CBSEL0 |

BANK2B |

G9 |

|

|

Pin 11 |

GPIOR_27 |

BANK2B |

H9 |

|

|

Pin 12 |

GPIOR_28 |

BANK2B |

J9 |

|

|

Pin 13 |

GPIOR_30 |

BANK2B |

J8 |

|

|

Pin 14 |

GPIOR_31 |

BANK2B |

G8 |

|

|

Pin 15 |

GPIOR_32 |

BANK2B |

H8 |

|

|

Pin 16 |

GPIOR_34_CSI |

BANK2B |

J7 |

|

|

Pin 17 |

GPIOR_35_CSO |

BANK2B |

G6 |

|

|

Pin 18 |

GPIOR_36 |

BANK2B |

H6 |

|

|

Pin 19 |

VCCIO2 |

|

|

BANK2B 用 I/O 電源 |

|

Pin 20 |

GND |

|

|

GND |

種類 |

ボード上の |

FPGA端子名 |

I/Oバンク |

端子位置 |

備考 |

|---|---|---|---|---|---|

ピン・ヘッダ J2 |

Pin 1 |

GND |

|

|

GND |

Pin 2 |

VCCIO1 |

|

|

BANK2A 用 I/O 電源 |

|

Pin 3 |

GPIOR_19_CLK6 |

BANK2A |

E8 |

|

|

Pin 4 |

GPIOR_18_CLK7 |

BANK2A |

D9 |

|

|

Pin 5 |

GPIOR_17_CTRL6_CBUS2 |

BANK2A |

D8 |

|

|

Pin 6 |

GPIOR_16_CTRL7_CBUS1 |

BANK2A |

D7 |

|

|

Pin 7 |

GPIOR_15_CBUS0 |

BANK2A |

C9 |

|

|

Pin 8 |

GPIOR_14 |

BANK2A |

B9 |

|

|

Pin 9 |

GPIOR_13 |

BANK2A |

D6 |

|

|

Pin 10 |

GPIOR_12 |

BANK2A |

C8 |

|

|

Pin 11 |

GPIOR_11 |

BANK2A |

B8 |

|

|

Pin 12 |

GPIOR_10 |

BANK2A |

A9 |

|

|

Pin 13 |

GPIOR_08 |

BANK2A |

A8 |

|

|

Pin 14 |

GPIOR_07 |

BANK2A |

C7 |

|

|

Pin 15 |

GPIOR_06 |

BANK2A |

C6 |

|

|

Pin 16 |

GPIOR_05 |

BANK2A |

B6 |

|

|

Pin 17 |

GPIOR_03 |

BANK2A |

A6 |

|

|

Pin 18 |

GPIOR_01 |

BANK2A |

B5 |

|

|

Pin 19 |

GPIOR_00 |

BANK2A |

A5 |

|

|

Pin 20 |

VBUS |

|

|

5V |

種類 |

ボード上の |

FPGA端子名 |

I/Oバンク |

端子位置 |

備考 |

|---|---|---|---|---|---|

PMOD ピン・ヘッダ J3 |

Pin 1 |

VBUS |

|

|

5V |

Pin 2 |

GPIOL_07_CDI6 |

BANK1A |

G3 |

|

|

Pin 3 PMOD_A_IO0 |

GPIOL_12_CTRL0 |

BANK1A |

G1 |

|

|

Pin 4 PMOD_A_IO1 |

GPIOL_13_CTRL1 |

BANK1A |

F1 |

|

|

Pin 5 PMOD_A_IO2 |

GPIOL_14_CLK0 |

BANK1A |

E2 |

|

|

Pin 6 PMOD_A_IO3 |

GPIOL_15_CLK1 |

BANK1A |

E1 |

|

|

Pin 7 PMOD_A_IO4 |

GPIOL_16_CLK2 |

BANK1B |

C2 |

|

|

Pin 8 PMOD_A_IO5 |

GPIOL_17_CLK3 |

BANK1B |

D2 |

|

|

Pin 9 PMOD_A_IO6 |

GPIOL_19_CTRL3 |

BANK1B |

D3 |

|

|

Pin 10 PMOD_A_IO7 |

GPIOL_18_CTRL2 |

BANK1B |

E3 |

|

|

Pin 11 GND |

GND |

|

|

GND |

|

Pin 12 GND |

GND |

|

|

GND |

|

Pin 13 VCC |

VCC |

|

|

3.3V |

|

Pin 14 VCC |

VCC |

|

|

3.3V |

種類 |

ボード上の |

FPGA端子名 |

I/Oバンク |

端子位置 |

備考 |

|---|---|---|---|---|---|

SD カード・スロット SD1 |

CD1 SD_DET |

GPIOL_07_CDI6 |

BANK1A |

G3 |

|

CD2 VCC |

|

|

|

3.3V |

|

G1 GND |

|

|

|

GND |

|

G2 GND |

|

|

|

GND |

|

G3 GND |

|

|

|

GND |

|

G4 GND |

|

|

|

GND |

|

T1 |

|

|

|

未接続 |

|

T2 SD_CS |

GPIOL_00 |

BANK1A |

G5 |

|

|

T3 SD_DI |

GPIOL_03_CDI4 |

BANK1A |

G4 |

|

|

T4 VCC |

|

|

|

3.3V |

|

T5 SD_SCLK |

GPIOL_09_CDI2 |

BANK1A |

J2 |

|

|

T6 GND |

|

|

|

GND |

|

T7 SD_DO |

GPIOL_05_CDI5 |

BANK1A |

J3 |

|

|

T8 |

|

|

|

未接続 |

以上、“ Xyloni ”入門[導入編]の前編をお送りいたしました。

後編ではFPGA統合化開発環境「Efinity」をインストールして、実践にうつっていきます!

後編にてご紹介していく内容は下記の予定です。

5 FPGA統合化開発環境Efinity のインストール(※後編にて公開中)

6 Xyloni ボードでLチカBlinkLED を設計しよう(※後編にて公開中)

7 FPGA統合環境Efinity でBlinkLED を実装しよう(※後編にて公開中)

後編もよろしくお願いいたします!

後編はこちらから

〈コアスタッフ〉

♦ Efinix(エフィニックス)製品の購入はこちらから

関連リンク

参考文献

[VOD/KIT]ARM Cortex-A9 & FPGA 内蔵SoC Zynq で初体験!オリジナル・プロセッサ開発入門

[1] Efinix Inc., Efinix Trion FPGA Overview, TRION-OVERVIEW-3.1, 2023

[2] Efinix Inc., Trion FPGA Selector Guide, TRION-SELECTOR-3.2, 2023

[3] Efinix Inc., T8 Data Sheet, DST8-v5.0, Oct.2023

[4] Efinix Inc., t8_pinout-v3.3.xlsx, Rev3.3, Sep.2023

[5] Efinix Inc., AN006: Configuring Trion FPGAs, AN006-v5.9, Sep.2023

[6] Efinix Inc., AN023: Using the Trion Power Estimator, AN023-v1.3, Sep.2022

[7] Efinix Inc., AN042: Working with PLLs, AN042-v1.0, Mar.2022

[8] Efinix Inc., AN046: Reset Guidelines for Efinix FPGAs, AN046-v1.1, Nov.2022

[9] Efinix Inc., Efinity Software Installation User Guide, UG-EFN-INSTALL-v2.9, Ma.r2023

[10] Efinix Inc., Efinity Software User Guide, UG-EFN-SOFTWARE-v12.1, Aug.2023

[11] Efinix Inc., Efinity Trion Tutorial, UG-EFN-TUTORIAL-v7.0, Aug.2022

[12] Efinix Inc., Trion Interfaces User Guide, UG-TiINTF-v3.2, Oct.2023

[13] Efinix Inc., Quantum Trion Primitives User Guide, UG-EFN-PRIMITIVES-v4.5, Jun.2023

[14] Efinix Inc., Efinity Synthesis User Guide, UG-EFN-SYNTH-v3.7, Jun.2023

[15] Efinix Inc., Efinity Timing Closure User Guide, UG-EFN-TIMING-v4.0, Jun.2023

[16] Efinix Inc., Efinity Python API, UG-EFN-PYAPI-v6.1, October 2023

[17] Efinix Inc., Efinity Programmer User Guide, UG-EFN-PGM-v2.9, Jun.2023

[18] Efinix Inc., AN050: Managing Windows Drivers, AN050-v1.1, Jul.2023

[19] Efinix Inc., Xyloni Development Kit Overview, XYLONI-DK-OVERVIEW-1.0, 2020

[20] Efinix Inc., Xyloni Development Kit User Guide, XYLONI-DK-UG-v1.4, Nov.2022

[21] Efinix Inc., Xyloni Development Board Schematics and BOM, XYLONI-SCHE, V1.06, Mar.2018

[22] Efinix Inc., Sapphire RISC-V SoC Data Sheet, DS-SAPPHIRE-v3.3, Jul.2023

[23] Efinix Inc., Sapphire RISC-V SoC Hardware and Software User Guide, UG-RISCV-SAPPHIRE-v5.3,Aug.2023

本稿の執筆には,本ページに記載のEfinix社のFPGAに関する技術資料を参照しました。いずれも同社ホームページの Support Center(https://www.efinixinc.com/support/index.php) から入手できます。各資料のバージョンは 2023年10月時点のものであり、頻繁に更新されているので、最新版を参照するようにしてください。